(筆記)CPU & Memory, Part 1: RAM

博文:https://chanjarster.github.io...git

原文:What every programmer should know about memory, Part 1, RAMgithub

1 Introduction

現在的計算機架構中CPU和main memory的訪問速度的差別是很大的,解決這一瓶頸有這麼幾種形式:網絡

- RAM硬件設計的改善(速度和並行)

- Memory controller設計

- CPU caches

- 給設備用的Direct memory access(DMA)

2 Commodity Hardware Today

大衆架構

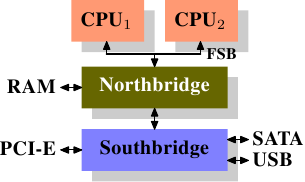

Figure 2.1: Structure with Northbridge and Southbridge架構

- 全部CPU經過FSB鏈接到北橋,北橋包含內存控制器(memory controller),鏈接到RAM。不一樣的內存類型如SRAM、DRAM有不一樣的內存控制器。

- 南橋又稱I/O橋,若是要訪問其餘系統設備,北橋必須和南橋通訊。南橋鏈接着各類不一樣的bus

這個架構要注意:併發

- CPU之間的全部數據通訊必須通過FSB,而這個FSB也是CPU和北橋通訊的bus。

- 全部和RAM的通訊都必須通過北橋

- RAM只有一個端口(port)

- CPU和掛接到南橋設備的通訊則有北橋路由

能夠發現瓶頸:ide

- 爲設備去訪問RAM的瓶頸。解決辦法是DMA,讓設備直接經過北橋訪問RAM,而不須要CPU的介入。現在掛到任一bus的全部高性能設備都能利用DMA。雖然DMA減小了CPU的工做量,可是爭用了北橋的帶寬

- 北橋到RAM的瓶頸。老的系統裏只有一條通往全部RAM芯片的bus。如今的RAM類型要求有兩條獨立的bus,因此倍增了帶寬(DDR2裏稱爲channel)。北橋經過多個channel交替訪問內存。

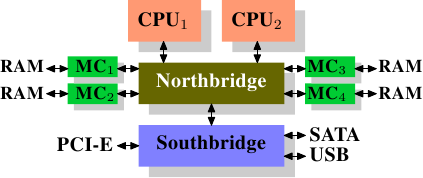

多內存控制器

比較貴的系統北橋本身不包含內存控制器,而是外接內存控制器:post

Figure 2.2: Northbridge with External Controllers性能

在這種架構裏有多個內存bus,大大增長了帶寬。在併發內存訪問的時候,能夠同時訪問不一樣的memory bank(我理解爲就是內存條)。而這個架構的瓶頸則是北橋內部的帶寬。spa

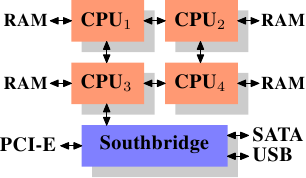

NUMA

除了使用多個內存控制器,還能夠採用下面的架構增長內存帶寬。作法就是把內存控制器內置在CPU裏。每一個CPU訪問本身的本地RAM。.net

Figure 2.3: Integrated Memory Controller

這個架構一樣也有缺點:由於這種系統裏的全部CPU仍是要可以訪問全部的RAM,因此the memory is not uniform anymore (hence the name NUMA - Non-Uniform Memory Architecture - for such an architecture)。訪問本地內存速度是正常的,訪問別的CPU的內存就不同了,CPU之間必須interconnect才行。在上圖中CPU1訪問CPU4的時候就要用到兩條interconnect。

2.1 RAM Types

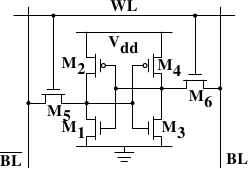

2.1.1 Static RAM

- 訪問SRAM沒有延遲,但SRAM貴,容量小。

Figure 2.4: 6-T Static RAM

電路圖就不解釋了。

2.2.1 Dynamic RAM

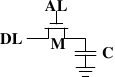

Figure 2.5: 1-T Dynamic RAM

電路圖就不解釋了。

- DRAM物理結構:若干RAM chip,RAM chip下有若干RAM cell,每一個RAM cell的狀態表明1 bit。

- 訪問DRAM有延遲(等待電容充放電),但DRAM便宜,容量大。商業機器廣泛使用DRAM,DDR之類的就是DRAM。

2.1.3 DRAM Access

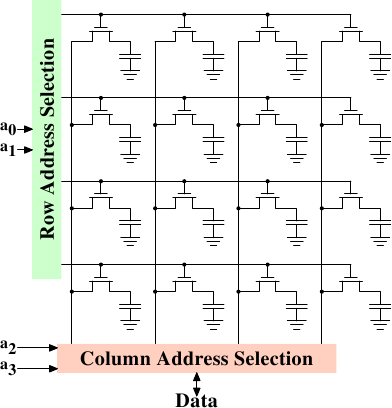

Figure 2.7: Dynamic RAM Schematic

訪問DRAM的步驟:

- RAS(Row address selection)

- CAS(Column address selection)

- 傳輸數據

RAS和CAS都須要消耗時鐘頻率,若是每次都須要從新RAS-CAS則性能會低。若是一次性把一行的數據都傳輸,則速度很快。

2.1.4 Conclusions

- 不是全部內存都是SRAM是有緣由的(成本緣由)

- memory cell必須被單獨選擇纔可以使用

- address line的數目直接影響到內存控制器、主板、DRAM module、DRAM chip的成本

- 須要等待一段時間才能獲得讀、寫操做的結果

2.2 DRAM Access Technical Details

略。

2.2.4 Memory Types

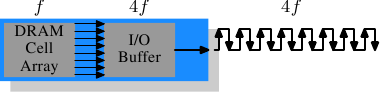

- 現代DRAM內置I/O buffer增長每次傳輸的數據量。

Figure 2.14: DDR3 SDRAM Operation

2.2.5 Conclusions

- 假如DRAM的時鐘頻率爲200MHz,I/O buffer每次傳送4份數據(商業宣傳其FSB爲800MHz),你的CPU是2GHz,那麼二者時鐘頻率則是1:10,意味着內存延遲1個時鐘頻率,那麼CPU就要等待10個時鐘頻率。

2.3 Other Main Memory Users

- 網絡控制器、大存儲控制器,使用DMA訪問內存。

- PCI-E卡也能經過南橋-北橋訪問內存。

- USB也用到FSB。

- 高DMA流量會佔用FSB,致使CPU訪問內存的時候等待時間變長。

- 在NUMA架構中,能夠CPU使用的內存不被DMA影響。在Section 6會詳細討論。

- 沒有獨立顯存的系統(會使用內存做爲顯寸),這種系統對於RAM的訪問會很頻繁,形成佔用FSB帶寬,影響系統性能。

- 1. (筆記)CPU & Memory, Part 2: CPU caches

- 2. CPU & Memory, Part 3: Virtual Memory

- 3. CPU & Memory, Part 4: NUMA support

- 4. 【簡記】Operating System—— memory management(part 1)

- 5. CPU學習筆記(1)

- 6. wpf datagrid筆記 part 1

- 7. 【學習筆記Part 1 ● Linux】

- 8. What every programmer should know about memory (Part 2-1) 譯

- 9. STM8學習筆記1:CPU簡介

- 10. How OpenResty and Nginx Shared Memory Zones Consume RAM

- 更多相關文章...

- • ASP.NET Razor - 標記 - ASP.NET 教程

- • ADO 刪除記錄 - ADO 教程

- • Tomcat學習筆記(史上最全tomcat學習筆記)

- • Docker容器實戰(六) - 容器的隔離與限制

-

每一个你不满意的现在,都有一个你没有努力的曾经。

- 1. (筆記)CPU & Memory, Part 2: CPU caches

- 2. CPU & Memory, Part 3: Virtual Memory

- 3. CPU & Memory, Part 4: NUMA support

- 4. 【簡記】Operating System—— memory management(part 1)

- 5. CPU學習筆記(1)

- 6. wpf datagrid筆記 part 1

- 7. 【學習筆記Part 1 ● Linux】

- 8. What every programmer should know about memory (Part 2-1) 譯

- 9. STM8學習筆記1:CPU簡介

- 10. How OpenResty and Nginx Shared Memory Zones Consume RAM